This is a work in progress for an NRF2401P

Dependents: NRF_receiver sender locker4 Weather_Station_Ofiicial ... more

About

This is a simple library to drive the nRF24l01+.

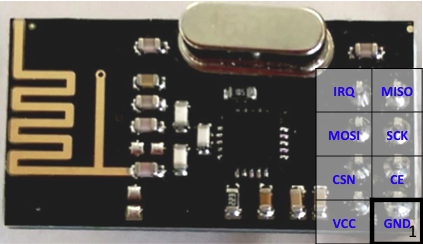

Hardware

This uses the commonly available breakout. The connections are shown below

Software

Use case: For a simple transmitter

tx code snipet

#include "NRF2401P.h"

int main() {

*

* long long addr1=0xAB00CD; // setup address - any 5 byte number - same as RX

* int channel =0x12; // [0-126] setup channel, must be same as RX

* bool txOK;

* char msg[32];

* char ackData[32];

* char len;

*

* // Setup

* NRF2401P nrf1(PTD6,PTD7, PTD5,PTD4, PTC12); //mosi, miso, sclk, csn, ce)

* nrf1.quickTxSetup(channel, addr1); // sets nrf24l01+ as transmitter

*

* // transmit

* strcpy (msg, "Hello");

* txOK= nrf1.transmitData(msg,strlen(msg));

*

* // read ack data if available

* if (nrf1.isAckData()) {

* len= nrf1.getRxData(ackData); // len is number of bytes in ackData

* }

*}

Use case: For a simple receiver

rx code snipet

#include "NRF2401P.h"

*int main(){

*

* long long addr1=0xAB00CD; // setup address - any 5 byte number - same as TX

* int channel =0x12; // [0-126] setup channel, must be same as TX

* bool txOK;

* char msg[32];

* char ackData[32];

* char len;

*

* // Setup

* NRF2401P nrf1(PTD6,PTD7, PTD5,PTD4, PTC12); //mosi, miso, sclk, csn, ce)

* nrf1.quickRxSetup(channel, addr1); // sets nrf24l01+ as receiver, using pipe 1

*

* // set ack data

* sprintf(ackData,"Ack data");

* nrf1.acknowledgeData(ackData, strlen(ackData),1); // ack for pipe 1

*

* // receive

* while (! nrf1.isRxData()); // note this blocks until RX data

* len= nrf1.getRxData(msg); // gets the message, len is length of msg

*

*}

nRF24l01.h@20:e61edde5680d, 2016-02-25 (annotated)

- Committer:

- epgmdm

- Date:

- Thu Feb 25 09:44:11 2016 +0000

- Revision:

- 20:e61edde5680d

- Parent:

- 2:ca0a3c0bba70

Minor updates to make all returns void if possible

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| epgmdm | 2:ca0a3c0bba70 | 1 | /* |

| epgmdm | 2:ca0a3c0bba70 | 2 | Copyright (c) 2007 Stefan Engelke <mbox@stefanengelke.de> |

| epgmdm | 2:ca0a3c0bba70 | 3 | Portions Copyright (C) 2011 Greg Copeland |

| epgmdm | 2:ca0a3c0bba70 | 4 | |

| epgmdm | 2:ca0a3c0bba70 | 5 | Permission is hereby granted, free of charge, to any person |

| epgmdm | 2:ca0a3c0bba70 | 6 | obtaining a copy of this software and associated documentation |

| epgmdm | 2:ca0a3c0bba70 | 7 | files (the "Software"), to deal in the Software without |

| epgmdm | 2:ca0a3c0bba70 | 8 | restriction, including without limitation the rights to use, copy, |

| epgmdm | 2:ca0a3c0bba70 | 9 | modify, merge, publish, distribute, sublicense, and/or sell copies |

| epgmdm | 2:ca0a3c0bba70 | 10 | of the Software, and to permit persons to whom the Software is |

| epgmdm | 2:ca0a3c0bba70 | 11 | furnished to do so, subject to the following conditions: |

| epgmdm | 2:ca0a3c0bba70 | 12 | |

| epgmdm | 2:ca0a3c0bba70 | 13 | The above copyright notice and this permission notice shall be |

| epgmdm | 2:ca0a3c0bba70 | 14 | included in all copies or substantial portions of the Software. |

| epgmdm | 2:ca0a3c0bba70 | 15 | |

| epgmdm | 2:ca0a3c0bba70 | 16 | THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, |

| epgmdm | 2:ca0a3c0bba70 | 17 | EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF |

| epgmdm | 2:ca0a3c0bba70 | 18 | MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND |

| epgmdm | 2:ca0a3c0bba70 | 19 | NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT |

| epgmdm | 2:ca0a3c0bba70 | 20 | HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, |

| epgmdm | 2:ca0a3c0bba70 | 21 | WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, |

| epgmdm | 2:ca0a3c0bba70 | 22 | OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER |

| epgmdm | 2:ca0a3c0bba70 | 23 | DEALINGS IN THE SOFTWARE. |

| epgmdm | 2:ca0a3c0bba70 | 24 | */ |

| epgmdm | 2:ca0a3c0bba70 | 25 | |

| epgmdm | 2:ca0a3c0bba70 | 26 | /* Memory Map */ |

| epgmdm | 2:ca0a3c0bba70 | 27 | #define CONFIG 0x00 |

| epgmdm | 2:ca0a3c0bba70 | 28 | #define EN_AA 0x01 |

| epgmdm | 2:ca0a3c0bba70 | 29 | #define EN_RXADDR 0x02 |

| epgmdm | 2:ca0a3c0bba70 | 30 | #define SETUP_AW 0x03 |

| epgmdm | 2:ca0a3c0bba70 | 31 | #define SETUP_RETR 0x04 |

| epgmdm | 2:ca0a3c0bba70 | 32 | #define RF_CH 0x05 |

| epgmdm | 2:ca0a3c0bba70 | 33 | #define RF_SETUP 0x06 |

| epgmdm | 2:ca0a3c0bba70 | 34 | #define STATUS 0x07 |

| epgmdm | 2:ca0a3c0bba70 | 35 | #define OBSERVE_TX 0x08 |

| epgmdm | 2:ca0a3c0bba70 | 36 | #define CD 0x09 |

| epgmdm | 2:ca0a3c0bba70 | 37 | #define RX_ADDR_P0 0x0A |

| epgmdm | 2:ca0a3c0bba70 | 38 | #define RX_ADDR_P1 0x0B |

| epgmdm | 2:ca0a3c0bba70 | 39 | #define RX_ADDR_P2 0x0C |

| epgmdm | 2:ca0a3c0bba70 | 40 | #define RX_ADDR_P3 0x0D |

| epgmdm | 2:ca0a3c0bba70 | 41 | #define RX_ADDR_P4 0x0E |

| epgmdm | 2:ca0a3c0bba70 | 42 | #define RX_ADDR_P5 0x0F |

| epgmdm | 2:ca0a3c0bba70 | 43 | #define TX_ADDR 0x10 |

| epgmdm | 2:ca0a3c0bba70 | 44 | #define RX_PW_P0 0x11 |

| epgmdm | 2:ca0a3c0bba70 | 45 | #define RX_PW_P1 0x12 |

| epgmdm | 2:ca0a3c0bba70 | 46 | #define RX_PW_P2 0x13 |

| epgmdm | 2:ca0a3c0bba70 | 47 | #define RX_PW_P3 0x14 |

| epgmdm | 2:ca0a3c0bba70 | 48 | #define RX_PW_P4 0x15 |

| epgmdm | 2:ca0a3c0bba70 | 49 | #define RX_PW_P5 0x16 |

| epgmdm | 2:ca0a3c0bba70 | 50 | #define FIFO_STATUS 0x17 |

| epgmdm | 2:ca0a3c0bba70 | 51 | #define DYNPD 0x1C |

| epgmdm | 2:ca0a3c0bba70 | 52 | #define FEATURE 0x1D |

| epgmdm | 2:ca0a3c0bba70 | 53 | |

| epgmdm | 2:ca0a3c0bba70 | 54 | /* Bit Mnemonics */ |

| epgmdm | 2:ca0a3c0bba70 | 55 | #define MASK_RX_DR 6 |

| epgmdm | 2:ca0a3c0bba70 | 56 | #define MASK_TX_DS 5 |

| epgmdm | 2:ca0a3c0bba70 | 57 | #define MASK_MAX_RT 4 |

| epgmdm | 2:ca0a3c0bba70 | 58 | #define EN_CRC 3 |

| epgmdm | 2:ca0a3c0bba70 | 59 | #define CRCO 2 |

| epgmdm | 2:ca0a3c0bba70 | 60 | #define PWR_UP 1 |

| epgmdm | 2:ca0a3c0bba70 | 61 | #define PRIM_RX 0 |

| epgmdm | 2:ca0a3c0bba70 | 62 | #define ENAA_P5 5 |

| epgmdm | 2:ca0a3c0bba70 | 63 | #define ENAA_P4 4 |

| epgmdm | 2:ca0a3c0bba70 | 64 | #define ENAA_P3 3 |

| epgmdm | 2:ca0a3c0bba70 | 65 | #define ENAA_P2 2 |

| epgmdm | 2:ca0a3c0bba70 | 66 | #define ENAA_P1 1 |

| epgmdm | 2:ca0a3c0bba70 | 67 | #define ENAA_P0 0 |

| epgmdm | 2:ca0a3c0bba70 | 68 | #define ERX_P5 5 |

| epgmdm | 2:ca0a3c0bba70 | 69 | #define ERX_P4 4 |

| epgmdm | 2:ca0a3c0bba70 | 70 | #define ERX_P3 3 |

| epgmdm | 2:ca0a3c0bba70 | 71 | #define ERX_P2 2 |

| epgmdm | 2:ca0a3c0bba70 | 72 | #define ERX_P1 1 |

| epgmdm | 2:ca0a3c0bba70 | 73 | #define ERX_P0 0 |

| epgmdm | 2:ca0a3c0bba70 | 74 | #define AW 0 |

| epgmdm | 2:ca0a3c0bba70 | 75 | #define ARD 4 |

| epgmdm | 2:ca0a3c0bba70 | 76 | #define ARC 0 |

| epgmdm | 2:ca0a3c0bba70 | 77 | #define PLL_LOCK 4 |

| epgmdm | 2:ca0a3c0bba70 | 78 | #define RF_DR 3 |

| epgmdm | 2:ca0a3c0bba70 | 79 | #define RF_PWR 6 |

| epgmdm | 2:ca0a3c0bba70 | 80 | #define RX_DR 6 |

| epgmdm | 2:ca0a3c0bba70 | 81 | #define TX_DS 5 |

| epgmdm | 2:ca0a3c0bba70 | 82 | #define MAX_RT 4 |

| epgmdm | 2:ca0a3c0bba70 | 83 | #define RX_P_NO 1 |

| epgmdm | 2:ca0a3c0bba70 | 84 | #define TX_FULL 0 |

| epgmdm | 2:ca0a3c0bba70 | 85 | #define PLOS_CNT 4 |

| epgmdm | 2:ca0a3c0bba70 | 86 | #define ARC_CNT 0 |

| epgmdm | 2:ca0a3c0bba70 | 87 | #define TX_REUSE 6 |

| epgmdm | 2:ca0a3c0bba70 | 88 | #define FIFO_FULL 5 |

| epgmdm | 2:ca0a3c0bba70 | 89 | #define TX_EMPTY 4 |

| epgmdm | 2:ca0a3c0bba70 | 90 | #define RX_FULL 1 |

| epgmdm | 2:ca0a3c0bba70 | 91 | #define RX_EMPTY 0 |

| epgmdm | 2:ca0a3c0bba70 | 92 | #define DPL_P5 5 |

| epgmdm | 2:ca0a3c0bba70 | 93 | #define DPL_P4 4 |

| epgmdm | 2:ca0a3c0bba70 | 94 | #define DPL_P3 3 |

| epgmdm | 2:ca0a3c0bba70 | 95 | #define DPL_P2 2 |

| epgmdm | 2:ca0a3c0bba70 | 96 | #define DPL_P1 1 |

| epgmdm | 2:ca0a3c0bba70 | 97 | #define DPL_P0 0 |

| epgmdm | 2:ca0a3c0bba70 | 98 | #define EN_DPL 2 |

| epgmdm | 2:ca0a3c0bba70 | 99 | #define EN_ACK_PAY 1 |

| epgmdm | 2:ca0a3c0bba70 | 100 | #define EN_DYN_ACK 0 |

| epgmdm | 2:ca0a3c0bba70 | 101 | |

| epgmdm | 2:ca0a3c0bba70 | 102 | /* Instruction Mnemonics */ |

| epgmdm | 2:ca0a3c0bba70 | 103 | #define R_REGISTER 0x00 |

| epgmdm | 2:ca0a3c0bba70 | 104 | #define W_REGISTER 0x20 |

| epgmdm | 2:ca0a3c0bba70 | 105 | #define REGISTER_MASK 0x1F |

| epgmdm | 2:ca0a3c0bba70 | 106 | #define ACTIVATE 0x50 |

| epgmdm | 2:ca0a3c0bba70 | 107 | #define R_RX_PL_WID 0x60 |

| epgmdm | 2:ca0a3c0bba70 | 108 | #define R_RX_PAYLOAD 0x61 |

| epgmdm | 2:ca0a3c0bba70 | 109 | #define W_TX_PAYLOAD 0xA0 |

| epgmdm | 2:ca0a3c0bba70 | 110 | #define W_ACK_PAYLOAD 0xA8 |

| epgmdm | 2:ca0a3c0bba70 | 111 | #define FLUSH_TX 0xE1 |

| epgmdm | 2:ca0a3c0bba70 | 112 | #define FLUSH_RX 0xE2 |

| epgmdm | 2:ca0a3c0bba70 | 113 | #define REUSE_TX_PL 0xE3 |

| epgmdm | 2:ca0a3c0bba70 | 114 | #define NOP 0xFF |

| epgmdm | 2:ca0a3c0bba70 | 115 | |

| epgmdm | 2:ca0a3c0bba70 | 116 | /* Non-P omissions */ |

| epgmdm | 2:ca0a3c0bba70 | 117 | #define LNA_HCURR 0 |

| epgmdm | 2:ca0a3c0bba70 | 118 | |

| epgmdm | 2:ca0a3c0bba70 | 119 | /* P model memory Map */ |

| epgmdm | 2:ca0a3c0bba70 | 120 | #define RPD 0x09 |

| epgmdm | 2:ca0a3c0bba70 | 121 | #define W_TX_PAYLOAD_NO_ACK 0xB0 |

| epgmdm | 2:ca0a3c0bba70 | 122 | |

| epgmdm | 2:ca0a3c0bba70 | 123 | /* P model bit Mnemonics */ |

| epgmdm | 2:ca0a3c0bba70 | 124 | #define RF_DR_LOW 5 |

| epgmdm | 2:ca0a3c0bba70 | 125 | #define RF_DR_HIGH 3 |

| epgmdm | 2:ca0a3c0bba70 | 126 | #define RF_PWR_LOW 1 |

| epgmdm | 2:ca0a3c0bba70 | 127 | #define RF_PWR_HIGH 2 |