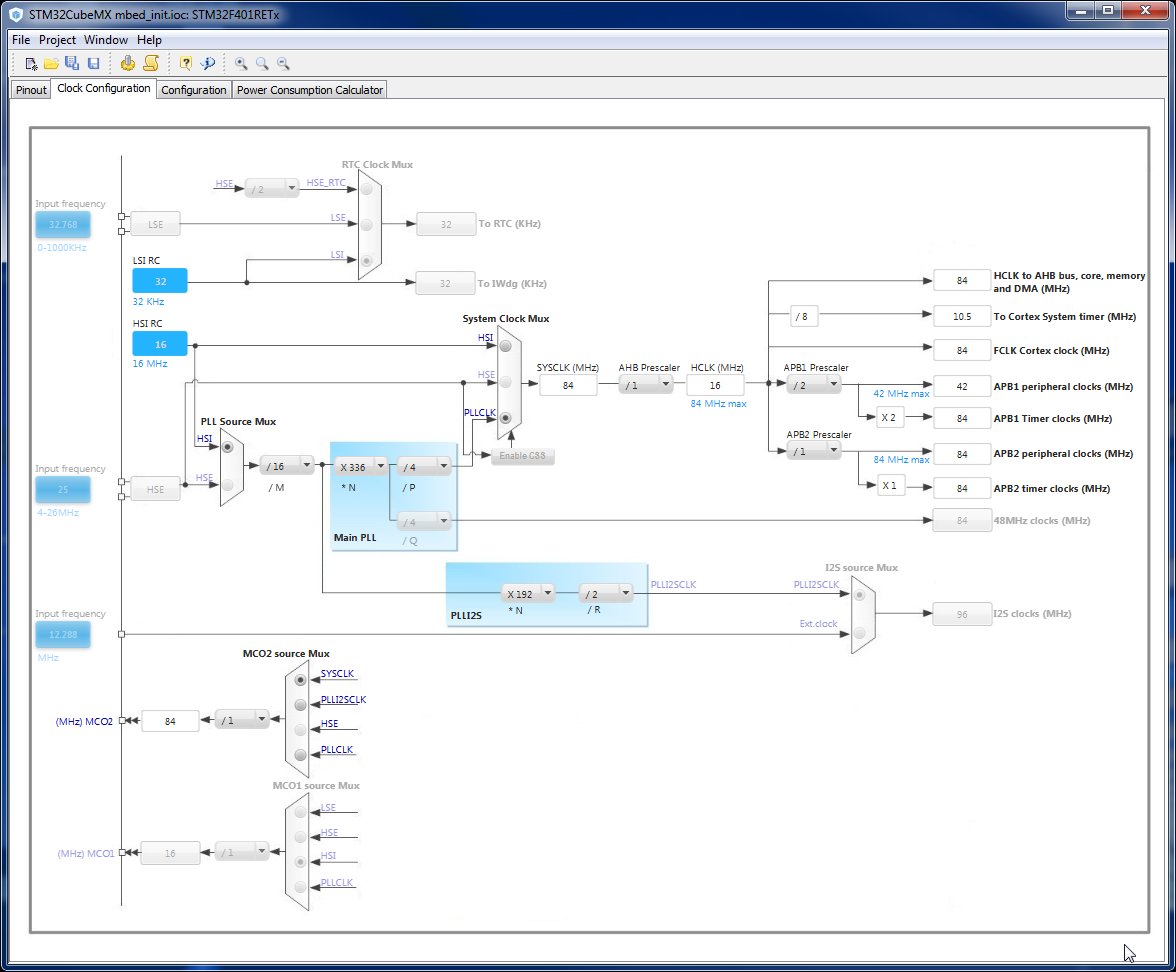

Lib to switch the clock speed of the ST Nucleo to 84MHz. The internal RC oscillator is multiplied with the PLL.

Dependents: Nucleo_spi_master_20MHz Nucleo_vs_Arduino_Speed_Test DMA_I2S_Test MPU9150AHRS ... more

Not needed with actual mbed lib

You don't need this lib to speed up the cpu clock. The actual mbed lib is using 84 MHz cpu speed out of the box.

The ST Nucleo board is running on 16 MHz out of the box. To speed up the cpu to the maximum speed we have to change the clock setting. Simply add

#include "ST_F401_84MHZ.h"

F401_init84 myinit(0);

in front of your program. This should be the first line in main to ensure the frequency is changed before other objects are initialised.

This frequency is generated out of the internal RC oscillator. The frequency is not so stable like a crystal ! My board is fluctuate +- 40KHz at 84MHz at room temperature.

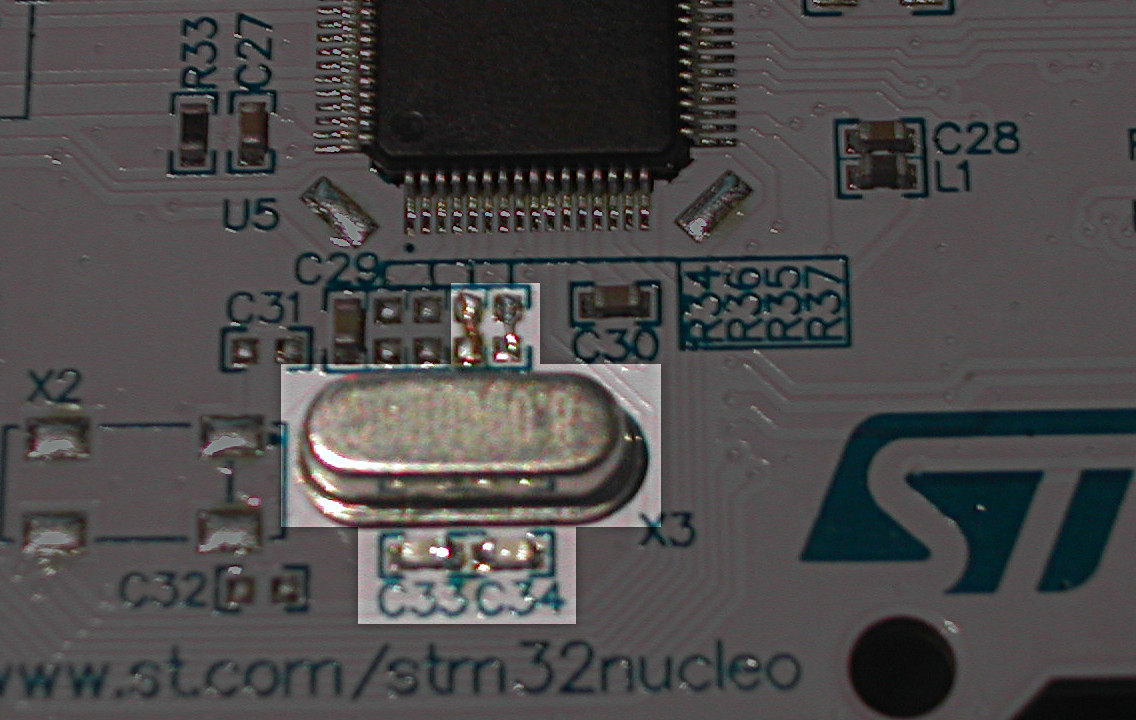

If you need a more precise timing source, you have to add a external crystal.

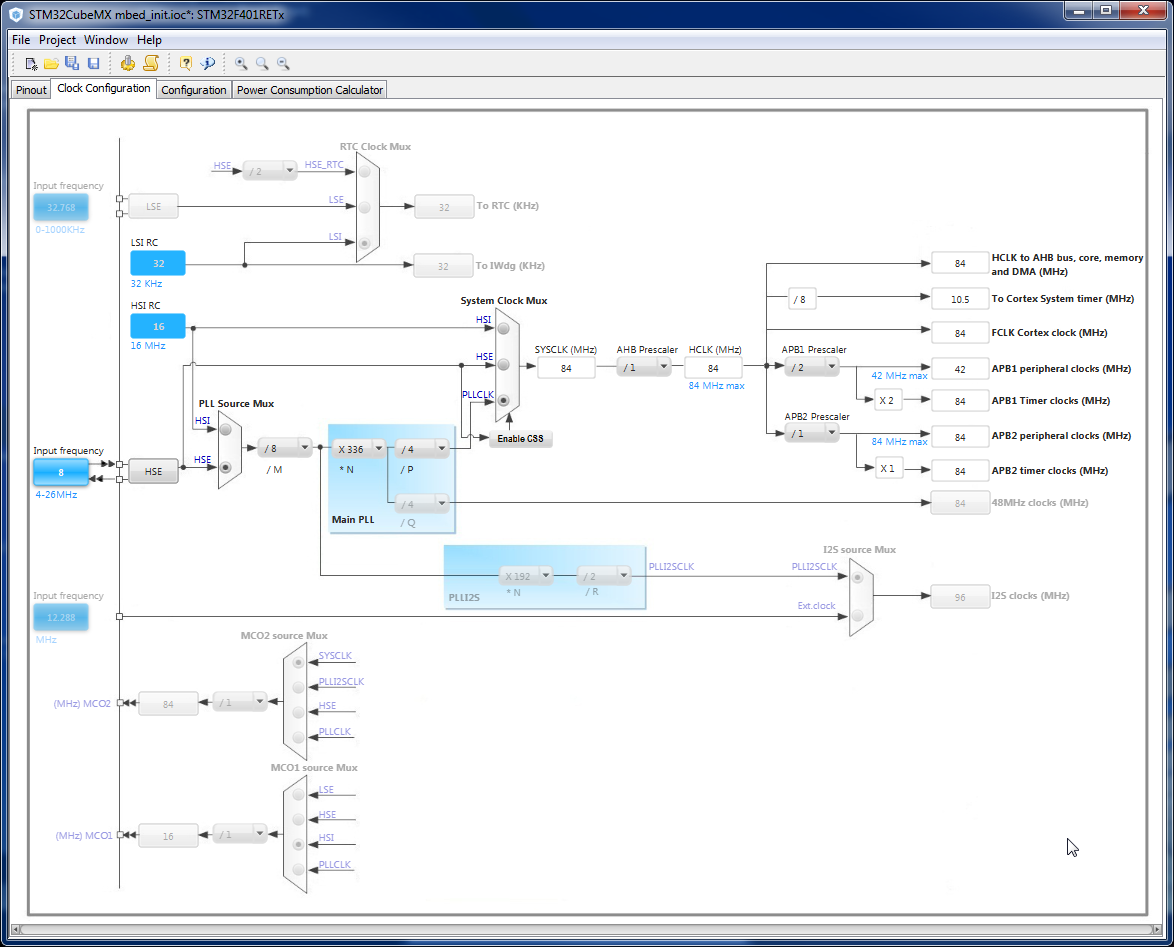

You need : X3 8MHz crystal , C33 and C34 18pF 0603 , R35 and R37 0R 0603 or you can simply use wire to short this two resistor pads. A call of SystemClock_Config_84MHz_external(); will config the pll to generate 84MHz out of the 8MHz crystal oscillator.

Add

#include "ST_F401_84MHZ.h"

F401_init84 myinit(1);

in front of your code to use the external 8MHz crystal.

If you want to use a different crystal or frequency : the STM32CubeMX tool is your friend :-)

external crystal value

The mbed lib is using HSE_VALUE defined in the file stm32f4xx_hal_config.h to calculate SystemCoreClock, which is used for all timings : baudrate or wait() ...

This value is the frequency of the external crystal.

It is defined to 25MHz at the moment I have asked to change it to 8MHz default.

You can set the variable SystemCoreClock to 84000000 to patch this .

If you use the internal oscillator the calculated value is ok

The value was changed to 8 MHz.

ST_F401_84MHZ.cpp@4:0834e0e36a1e, 2014-03-07 (annotated)

- Committer:

- dreschpe

- Date:

- Fri Mar 07 21:23:07 2014 +0000

- Revision:

- 4:0834e0e36a1e

- Parent:

- 3:1d8106fcb4c5

- Child:

- 5:f44655076466

docu

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| dreschpe | 0:e54167eaccc6 | 1 | // use the STM32CubeMX Tool to calculate the register settings |

| dreschpe | 0:e54167eaccc6 | 2 | // www.st.com/stm32cube |

| dreschpe | 0:e54167eaccc6 | 3 | // |

| dreschpe | 0:e54167eaccc6 | 4 | |

| dreschpe | 0:e54167eaccc6 | 5 | #include "stm32f4xx_hal.h" |

| dreschpe | 0:e54167eaccc6 | 6 | |

| dreschpe | 1:d19543ab3afa | 7 | void SystemClock_Config_84MHz_internal(void) |

| dreschpe | 0:e54167eaccc6 | 8 | { |

| dreschpe | 0:e54167eaccc6 | 9 | RCC_ClkInitTypeDef RCC_ClkInitStruct; |

| dreschpe | 0:e54167eaccc6 | 10 | RCC_OscInitTypeDef RCC_OscInitStruct; |

| dreschpe | 0:e54167eaccc6 | 11 | |

| dreschpe | 0:e54167eaccc6 | 12 | RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSI; // internal 16MHz RC |

| dreschpe | 0:e54167eaccc6 | 13 | RCC_OscInitStruct.HSIState = RCC_HSI_ON; |

| dreschpe | 0:e54167eaccc6 | 14 | RCC_OscInitStruct.HSICalibrationValue = 6; |

| dreschpe | 0:e54167eaccc6 | 15 | RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON; // PLL on |

| dreschpe | 0:e54167eaccc6 | 16 | RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSI; |

| dreschpe | 0:e54167eaccc6 | 17 | RCC_OscInitStruct.PLL.PLLM = 16; // setup PLL divider |

| dreschpe | 0:e54167eaccc6 | 18 | RCC_OscInitStruct.PLL.PLLN = 336; |

| dreschpe | 0:e54167eaccc6 | 19 | RCC_OscInitStruct.PLL.PLLP = RCC_PLLP_DIV4; |

| dreschpe | 0:e54167eaccc6 | 20 | RCC_OscInitStruct.PLL.PLLQ = 4; |

| dreschpe | 0:e54167eaccc6 | 21 | HAL_RCC_OscConfig(&RCC_OscInitStruct); |

| dreschpe | 0:e54167eaccc6 | 22 | |

| dreschpe | 0:e54167eaccc6 | 23 | RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_SYSCLK|RCC_CLOCKTYPE_PCLK1; |

| dreschpe | 0:e54167eaccc6 | 24 | RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK; |

| dreschpe | 0:e54167eaccc6 | 25 | RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV2; |

| dreschpe | 0:e54167eaccc6 | 26 | HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_2); |

| dreschpe | 3:1d8106fcb4c5 | 27 | SystemCoreClockUpdate(); // update SystemCoreClock var |

| dreschpe | 2:e5c1060ec62d | 28 | } |

| dreschpe | 2:e5c1060ec62d | 29 | |

| dreschpe | 2:e5c1060ec62d | 30 | |

| dreschpe | 2:e5c1060ec62d | 31 | // use a external 8 MHz crystal to generate the CPU clock |

| dreschpe | 2:e5c1060ec62d | 32 | // You have to add X3 8MHz |

| dreschpe | 2:e5c1060ec62d | 33 | // C33,C34 18pF 0603 |

| dreschpe | 2:e5c1060ec62d | 34 | // R35,R37 0R 0603 or use wire |

| dreschpe | 4:0834e0e36a1e | 35 | |

| dreschpe | 4:0834e0e36a1e | 36 | |

| dreschpe | 2:e5c1060ec62d | 37 | void SystemClock_Config_84MHz_external(void) |

| dreschpe | 2:e5c1060ec62d | 38 | { |

| dreschpe | 2:e5c1060ec62d | 39 | RCC_ClkInitTypeDef RCC_ClkInitStruct; |

| dreschpe | 2:e5c1060ec62d | 40 | RCC_OscInitTypeDef RCC_OscInitStruct; |

| dreschpe | 2:e5c1060ec62d | 41 | |

| dreschpe | 2:e5c1060ec62d | 42 | RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_LSI|RCC_OSCILLATORTYPE_HSE; |

| dreschpe | 2:e5c1060ec62d | 43 | RCC_OscInitStruct.HSEState = RCC_HSE_ON; |

| dreschpe | 2:e5c1060ec62d | 44 | RCC_OscInitStruct.LSIState = RCC_LSI_ON; |

| dreschpe | 2:e5c1060ec62d | 45 | RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON; |

| dreschpe | 2:e5c1060ec62d | 46 | RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE; |

| dreschpe | 2:e5c1060ec62d | 47 | RCC_OscInitStruct.PLL.PLLM = 8; |

| dreschpe | 2:e5c1060ec62d | 48 | RCC_OscInitStruct.PLL.PLLN = 336; |

| dreschpe | 2:e5c1060ec62d | 49 | RCC_OscInitStruct.PLL.PLLP = RCC_PLLP_DIV4; |

| dreschpe | 2:e5c1060ec62d | 50 | RCC_OscInitStruct.PLL.PLLQ = 4; |

| dreschpe | 2:e5c1060ec62d | 51 | HAL_RCC_OscConfig(&RCC_OscInitStruct); |

| dreschpe | 2:e5c1060ec62d | 52 | |

| dreschpe | 2:e5c1060ec62d | 53 | RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_SYSCLK|RCC_CLOCKTYPE_PCLK1; |

| dreschpe | 2:e5c1060ec62d | 54 | RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK; |

| dreschpe | 2:e5c1060ec62d | 55 | RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV2; |

| dreschpe | 2:e5c1060ec62d | 56 | HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_2); |

| dreschpe | 3:1d8106fcb4c5 | 57 | SystemCoreClockUpdate(); // update SystemCoreClock var |

| dreschpe | 2:e5c1060ec62d | 58 | |

| dreschpe | 2:e5c1060ec62d | 59 | } |