Library to handle the X-NUCLEO-CCA01M1 Sound Terminal Expansion Board.

Dependencies: ST_I2S X_NUCLEO_COMMON

Dependents: HelloWorld_CCA01M1 HelloWorld_CCA01M1_mbedOS HelloWorld_CCA01M1_mbedOS Karaoke_CCA01M1_CCA02M1_mbedOS ... more

Fork of X_NUCLEO_CCA01M1 by

Sound Terminal Library

Library to handle the X-NUCLEO-CCA01M1 Sound Terminal Expansion Board based on the STA350BW Sound Terminal device. A single board allows the output of a standard 2-channel stereo signal, while two boards stacked up realize a 4-channel audio system.

Power supply

The X-NUCLEO-CCA01M1 Sound Terminal Expansion Board has to be powered with at least 5V DC. You can connect the VCC terminal to an external power supplier or directly to the +5V pin of the CN6 Arduino connector.

Platform compatibility

- This board can be currently used with the Nucleo F4 Family only, please see the ST_I2S library compatibility for further information.

- The library is compatible both with mbed OS 5.x and mbed classic 2.x (to work with mbed classic, the main application has to import the "events" library, which is not included into the "mbed" library).

I2S Peripheral Usage

This board makes use of an I2S peripheral available on Nucleo boards, and when stacked up two times on the same Nucleo board each expansion board have to be configured to use a different I2S peripheral.

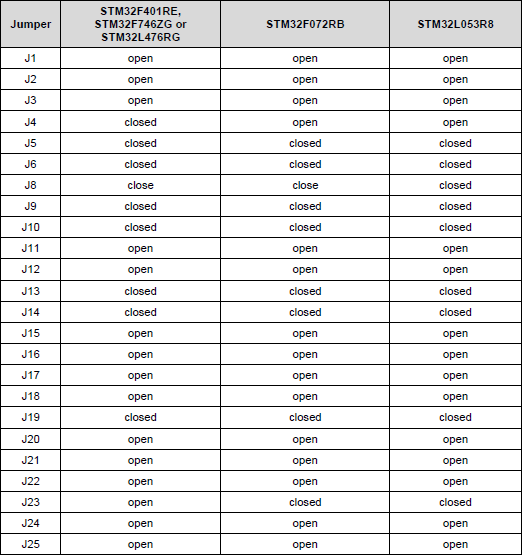

By default it comes with solder bridges configured to use the I2S1 peripheral, as depicted here below:

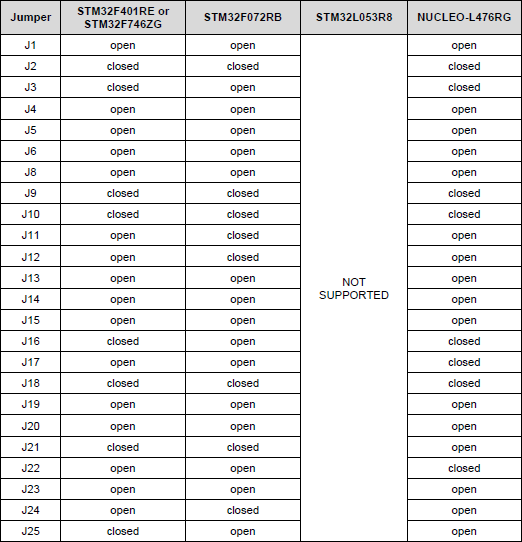

And can be set to use the I2S2 peripheral by configuring the solder bridges this way:

Components/STA350BW/STA350BW_def.h@5:2d450bbee471, 2017-04-21 (annotated)

- Committer:

- Davidroid

- Date:

- Fri Apr 21 08:15:15 2017 +0000

- Revision:

- 5:2d450bbee471

- Parent:

- Components/sta350bw/STA350BW_def.h@4:77a26607bef6

- Child:

- 7:b98581eae911

Aligned to ARM mbed coding style.

Who changed what in which revision?

| User | Revision | Line number | New contents of line |

|---|---|---|---|

| davide.aliprandi@st.com | 4:77a26607bef6 | 1 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 2 | ****************************************************************************** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 3 | * @file STA350BW_def.h |

| davide.aliprandi@st.com | 4:77a26607bef6 | 4 | * @author Central Labs |

| davide.aliprandi@st.com | 4:77a26607bef6 | 5 | * @version V1.0.0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 6 | * @date 18-August-2015 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 7 | * @brief This file contains definitions for STA350BW.c |

| davide.aliprandi@st.com | 4:77a26607bef6 | 8 | * firmware driver. |

| davide.aliprandi@st.com | 4:77a26607bef6 | 9 | ****************************************************************************** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 10 | * @attention |

| davide.aliprandi@st.com | 4:77a26607bef6 | 11 | * |

| davide.aliprandi@st.com | 4:77a26607bef6 | 12 | * <h2><center>© COPYRIGHT(c) 2014 STMicroelectronics</center></h2> |

| davide.aliprandi@st.com | 4:77a26607bef6 | 13 | * |

| davide.aliprandi@st.com | 4:77a26607bef6 | 14 | * Redistribution and use in source and binary forms, with or without modification, |

| davide.aliprandi@st.com | 4:77a26607bef6 | 15 | * are permitted provided that the following conditions are met: |

| davide.aliprandi@st.com | 4:77a26607bef6 | 16 | * 1. Redistributions of source code must retain the above copyright notice, |

| davide.aliprandi@st.com | 4:77a26607bef6 | 17 | * this list of conditions and the following disclaimer. |

| davide.aliprandi@st.com | 4:77a26607bef6 | 18 | * 2. Redistributions in binary form must reproduce the above copyright notice, |

| davide.aliprandi@st.com | 4:77a26607bef6 | 19 | * this list of conditions and the following disclaimer in the documentation |

| davide.aliprandi@st.com | 4:77a26607bef6 | 20 | * and/or other materials provided with the distribution. |

| davide.aliprandi@st.com | 4:77a26607bef6 | 21 | * 3. Neither the name of STMicroelectronics nor the names of its contributors |

| davide.aliprandi@st.com | 4:77a26607bef6 | 22 | * may be used to endorse or promote products derived from this software |

| davide.aliprandi@st.com | 4:77a26607bef6 | 23 | * without specific prior written permission. |

| davide.aliprandi@st.com | 4:77a26607bef6 | 24 | * |

| davide.aliprandi@st.com | 4:77a26607bef6 | 25 | * THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" |

| davide.aliprandi@st.com | 4:77a26607bef6 | 26 | * AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE |

| davide.aliprandi@st.com | 4:77a26607bef6 | 27 | * IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE |

| davide.aliprandi@st.com | 4:77a26607bef6 | 28 | * DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE |

| davide.aliprandi@st.com | 4:77a26607bef6 | 29 | * FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL |

| davide.aliprandi@st.com | 4:77a26607bef6 | 30 | * DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR |

| davide.aliprandi@st.com | 4:77a26607bef6 | 31 | * SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER |

| davide.aliprandi@st.com | 4:77a26607bef6 | 32 | * CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, |

| davide.aliprandi@st.com | 4:77a26607bef6 | 33 | * OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE |

| davide.aliprandi@st.com | 4:77a26607bef6 | 34 | * OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. |

| davide.aliprandi@st.com | 4:77a26607bef6 | 35 | * |

| davide.aliprandi@st.com | 4:77a26607bef6 | 36 | ****************************************************************************** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 37 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 38 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 39 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 40 | /* Define to prevent recursive inclusion -------------------------------------*/ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 41 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 42 | #ifndef __STA350BW_H |

| davide.aliprandi@st.com | 4:77a26607bef6 | 43 | #define __STA350BW_H |

| davide.aliprandi@st.com | 4:77a26607bef6 | 44 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 45 | #ifdef __cplusplus |

| davide.aliprandi@st.com | 4:77a26607bef6 | 46 | extern "C" { |

| davide.aliprandi@st.com | 4:77a26607bef6 | 47 | #endif |

| davide.aliprandi@st.com | 4:77a26607bef6 | 48 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 49 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 50 | /* Includes ------------------------------------------------------------------*/ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 51 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 52 | #include "../Common/sound_terminal.h" |

| davide.aliprandi@st.com | 4:77a26607bef6 | 53 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 54 | /** @addtogroup BSP |

| davide.aliprandi@st.com | 4:77a26607bef6 | 55 | * @{ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 56 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 57 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 58 | /** @addtogroup Components |

| davide.aliprandi@st.com | 4:77a26607bef6 | 59 | * @{ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 60 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 61 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 62 | /** @addtogroup STA350BW |

| davide.aliprandi@st.com | 4:77a26607bef6 | 63 | * @{ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 64 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 65 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 66 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 67 | /** @defgroup STA350BW_Exported_Constants |

| davide.aliprandi@st.com | 4:77a26607bef6 | 68 | * @{ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 69 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 70 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 71 | /** @defgroup STA350BW_Registers_Mapping |

| davide.aliprandi@st.com | 4:77a26607bef6 | 72 | * @brief STA350BW register mapping |

| davide.aliprandi@st.com | 4:77a26607bef6 | 73 | * @{ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 74 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 75 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 76 | #define STA350BW_MAX_REGISTERS ((uint8_t)0x56) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 77 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 78 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 79 | * @brief Configuration Register A |

| davide.aliprandi@st.com | 4:77a26607bef6 | 80 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 81 | * Read/Write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 82 | * Default value: 0x63 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 83 | * 7 FAULT detect recovery bypass |

| davide.aliprandi@st.com | 4:77a26607bef6 | 84 | * 6 TWAB Thermal warning adjustable bypass |

| davide.aliprandi@st.com | 4:77a26607bef6 | 85 | * 5 TWRB Thermal warning recovery bypass |

| davide.aliprandi@st.com | 4:77a26607bef6 | 86 | * 4,3 IR Interpolatio ratio |

| davide.aliprandi@st.com | 4:77a26607bef6 | 87 | * [2:0] MCS Master clock selection |

| davide.aliprandi@st.com | 4:77a26607bef6 | 88 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 89 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 90 | #define STA350BW_CONF_REGA ((uint8_t)0x00) /*Configuration Register A*/ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 91 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 92 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 93 | * @brief Configuration Register B |

| davide.aliprandi@st.com | 4:77a26607bef6 | 94 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 95 | * Read/Write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 96 | * Default value: 0x80 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 97 | * 7 C2IM channel 2 input mapping |

| davide.aliprandi@st.com | 4:77a26607bef6 | 98 | * 6 C2IM channel 1 input mapping |

| davide.aliprandi@st.com | 4:77a26607bef6 | 99 | * 5 DSCKE Delay serial clock enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 100 | * 4 SAIFB Serial data first bit |

| davide.aliprandi@st.com | 4:77a26607bef6 | 101 | * [3:0] Serial Input interface format |

| davide.aliprandi@st.com | 4:77a26607bef6 | 102 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 103 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 104 | #define STA350BW_CONF_REGB ((uint8_t)0x01) /*Configuration Register B*/ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 105 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 106 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 107 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 108 | * @brief Configuration Register C |

| davide.aliprandi@st.com | 4:77a26607bef6 | 109 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 110 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 111 | * Default value: 0x09F |

| davide.aliprandi@st.com | 4:77a26607bef6 | 112 | * 7 OCRB Overcurrent warning adjustment bypass |

| davide.aliprandi@st.com | 4:77a26607bef6 | 113 | * [5:2] CSZx: FFX compensating pulse size |

| davide.aliprandi@st.com | 4:77a26607bef6 | 114 | * [1:0] OMx: FFX Output mode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 115 | * 0 Clk_Out: Enable HSE on MCO. 0: MCO disable. 1: MCO enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 116 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 117 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 118 | #define STA350BW_CONF_REGC ((uint8_t)0x02) /*Configuration Register C*/ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 119 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 120 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 121 | * @brief I2C address Configuration Register D |

| davide.aliprandi@st.com | 4:77a26607bef6 | 122 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 123 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 124 | * Default value: 0x40 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 125 | * 7 SME soft mute enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 126 | * 6 ZDE zero detect enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 127 | * 5 DRC DRC or anti-clipping mode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 128 | * 4 BQL Biquad Link |

| davide.aliprandi@st.com | 4:77a26607bef6 | 129 | * 3 PSL Post scale Link |

| davide.aliprandi@st.com | 4:77a26607bef6 | 130 | * 2 DSPB DSP bypass |

| davide.aliprandi@st.com | 4:77a26607bef6 | 131 | * 1 DEMP De-Emphasys filter |

| davide.aliprandi@st.com | 4:77a26607bef6 | 132 | * 0 HPB High pass filter bypass |

| davide.aliprandi@st.com | 4:77a26607bef6 | 133 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 134 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 135 | #define STA350BW_CONF_REGD ((uint8_t)0x03) /*Configuration Register D*/ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 136 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 137 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 138 | * @brief I2C address Configuration Register E |

| davide.aliprandi@st.com | 4:77a26607bef6 | 139 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 140 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 141 | * Default value: 0xC2 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 142 | * 7 SVE soft volume enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 143 | * 6 ZCE zero crossing enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 144 | * 5 DCCV variable distorsion compensation |

| davide.aliprandi@st.com | 4:77a26607bef6 | 145 | * 4 PWMS PWM speed |

| davide.aliprandi@st.com | 4:77a26607bef6 | 146 | * 3 AME AM noise reduction enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 147 | * 2 NSBW Noise shaper bandwidth |

| davide.aliprandi@st.com | 4:77a26607bef6 | 148 | * 1 MPC Max Power correction |

| davide.aliprandi@st.com | 4:77a26607bef6 | 149 | * 0 MPCV Variable ax power correction |

| davide.aliprandi@st.com | 4:77a26607bef6 | 150 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 151 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 152 | #define STA350BW_CONF_REGE ((uint8_t)0x04) /*Configuration Register E*/ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 153 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 154 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 155 | * @brief I2C address Configuration Register F |

| davide.aliprandi@st.com | 4:77a26607bef6 | 156 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 157 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 158 | * Default value: 0x5C |

| davide.aliprandi@st.com | 4:77a26607bef6 | 159 | * 7 EAPD External Amplifier Power Down |

| davide.aliprandi@st.com | 4:77a26607bef6 | 160 | * 6 PWDN device power down |

| davide.aliprandi@st.com | 4:77a26607bef6 | 161 | * 5 ECLE Auto EAPD on clock loss |

| davide.aliprandi@st.com | 4:77a26607bef6 | 162 | * 4 LDTE LRCK double trigger protection |

| davide.aliprandi@st.com | 4:77a26607bef6 | 163 | * 3 BCLE Binary out mode clock loss detection |

| davide.aliprandi@st.com | 4:77a26607bef6 | 164 | * 2 IDE Invalid Input Detect |

| davide.aliprandi@st.com | 4:77a26607bef6 | 165 | * 1,0 OCFG Output configuration |

| davide.aliprandi@st.com | 4:77a26607bef6 | 166 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 167 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 168 | #define STA350BW_CONF_REGF ((uint8_t)0x05) /*Configuration Register F*/ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 169 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 170 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 171 | * @brief I2C address MUTE/Line Out configuration |

| davide.aliprandi@st.com | 4:77a26607bef6 | 172 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 173 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 174 | * Default value: 0x10 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 175 | * [7:6] LOC line out configuration |

| davide.aliprandi@st.com | 4:77a26607bef6 | 176 | * [5:4] RESERVED |

| davide.aliprandi@st.com | 4:77a26607bef6 | 177 | * 3 C3M Channel 3 MUTE |

| davide.aliprandi@st.com | 4:77a26607bef6 | 178 | * 2 C2M Channel 2 MUTE |

| davide.aliprandi@st.com | 4:77a26607bef6 | 179 | * 1 C1M Channel 1 MUTE |

| davide.aliprandi@st.com | 4:77a26607bef6 | 180 | * 0 MMUTE Master Mute |

| davide.aliprandi@st.com | 4:77a26607bef6 | 181 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 182 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 183 | #define STA350BW_MUTE ((uint8_t)0x06) /* MUTE / Lineout configuration */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 184 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 185 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 186 | * @brief I2C address Master Volume |

| davide.aliprandi@st.com | 4:77a26607bef6 | 187 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 188 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 189 | * Default value: 0xFF |

| davide.aliprandi@st.com | 4:77a26607bef6 | 190 | * [7:0] Master volume (default -127.5dB) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 191 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 192 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 193 | #define STA350BW_MVOL ((uint8_t)0x07) /* Master Volume */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 194 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 195 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 196 | * @brief I2C address Channel 1 Volume |

| davide.aliprandi@st.com | 4:77a26607bef6 | 197 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 198 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 199 | * Default value: 0x60 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 200 | * [7:0] Master volume (default 0.0dB) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 201 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 202 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 203 | #define STA350BW_C1VOL ((uint8_t)0x08) /* Channel 1 volume */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 204 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 205 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 206 | * @brief I2C address Channel 2 Volume |

| davide.aliprandi@st.com | 4:77a26607bef6 | 207 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 208 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 209 | * Default value: 0x60 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 210 | * [7:0] Master volume (default 0.0dB) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 211 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 212 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 213 | #define STA350BW_C2VOL ((uint8_t)0x09) /* Channel 2 volume */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 214 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 215 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 216 | * @brief I2C address Channel 3 Volume |

| davide.aliprandi@st.com | 4:77a26607bef6 | 217 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 218 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 219 | * Default value: 0x60 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 220 | * [7:0] Master volume (default 0.0dB) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 221 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 222 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 223 | #define STA350BW_C3VOL ((uint8_t)0x0A) /* Channel 3 volume */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 224 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 225 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 226 | * @brief I2C address AUTO MODE 1 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 227 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 228 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 229 | * Default value: 0x80 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 230 | * [7:6] RESERVED |

| davide.aliprandi@st.com | 4:77a26607bef6 | 231 | * [5:4] AMGC Audio Preset Gain compression |

| davide.aliprandi@st.com | 4:77a26607bef6 | 232 | * [3:0] RESERVED |

| davide.aliprandi@st.com | 4:77a26607bef6 | 233 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 234 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 235 | #define STA350BW_AUTO1 ((uint8_t)0x0B) /* Audio Preset 1 register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 236 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 237 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 238 | * @brief I2C address AUTO MODE 2 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 239 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 240 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 241 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 242 | * [7:4] XO preset crossover filter |

| davide.aliprandi@st.com | 4:77a26607bef6 | 243 | * [3:1] AMAMx AM atomode settings |

| davide.aliprandi@st.com | 4:77a26607bef6 | 244 | * 0 AMAME AM automode enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 245 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 246 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 247 | #define STA350BW_AUTO2 ((uint8_t)0x0C) /* Audio Preset 2 register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 248 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 249 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 250 | * @brief I2C address Channel 1 configuration register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 251 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 252 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 253 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 254 | * 7,6 C1OM Channel 1 output mapping |

| davide.aliprandi@st.com | 4:77a26607bef6 | 255 | * 5,4 C1LS Channel 1 limiter mapping |

| davide.aliprandi@st.com | 4:77a26607bef6 | 256 | * 3 C1BO Channel 1 Binary output |

| davide.aliprandi@st.com | 4:77a26607bef6 | 257 | * 2 C1VPB Channel 1 volume bypass |

| davide.aliprandi@st.com | 4:77a26607bef6 | 258 | * 1 C1EQBP Channel 1 Equalization Bypass |

| davide.aliprandi@st.com | 4:77a26607bef6 | 259 | * 0 C1TCB Channel 1 Tone/Control Bypass |

| davide.aliprandi@st.com | 4:77a26607bef6 | 260 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 261 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 262 | #define STA350BW_C1CFG ((uint8_t)0x0E) /* Channel 1 configuration register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 263 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 264 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 265 | * @brief I2C address Channel 2 configuration register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 266 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 267 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 268 | * Default value: 0x40 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 269 | * 7,6 C2OM Channel 2 output mapping |

| davide.aliprandi@st.com | 4:77a26607bef6 | 270 | * 5,4 C2LS Channel 2 limiter mapping |

| davide.aliprandi@st.com | 4:77a26607bef6 | 271 | * 3 C2BO Channel 2 Binary output |

| davide.aliprandi@st.com | 4:77a26607bef6 | 272 | * 2 C2VPB Channel 2 volume bypass |

| davide.aliprandi@st.com | 4:77a26607bef6 | 273 | * 1 C2EQBP Channel 2 Equalization Bypass |

| davide.aliprandi@st.com | 4:77a26607bef6 | 274 | * 0 C2TCB Channel 2 Tone/Control Bypass |

| davide.aliprandi@st.com | 4:77a26607bef6 | 275 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 276 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 277 | #define STA350BW_C2CFG ((uint8_t)0x0F) /* Channel 2 configuration register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 278 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 279 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 280 | * @brief I2C address Channel 3 configuration register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 281 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 282 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 283 | * Default value: 0x80 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 284 | * 7,6 C2OM Channel 3 output mapping |

| davide.aliprandi@st.com | 4:77a26607bef6 | 285 | * 5,4 C2LS Channel 3 limiter mapping |

| davide.aliprandi@st.com | 4:77a26607bef6 | 286 | * 3 C2BO Channel 3 Binary output |

| davide.aliprandi@st.com | 4:77a26607bef6 | 287 | * 2 C2VPB Channel 3 volume bypass |

| davide.aliprandi@st.com | 4:77a26607bef6 | 288 | * 1,0 RESERVED |

| davide.aliprandi@st.com | 4:77a26607bef6 | 289 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 290 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 291 | #define STA350BW_C3CFG ((uint8_t)0x10) /* Channel 3 configuration register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 292 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 293 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 294 | * @brief I2C address Tone control register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 295 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 296 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 297 | * Default value: 0x77 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 298 | * [7:4] Treble |

| davide.aliprandi@st.com | 4:77a26607bef6 | 299 | * [3:0] Bass |

| davide.aliprandi@st.com | 4:77a26607bef6 | 300 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 301 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 302 | #define STA350BW_TONE ((uint8_t)0x11) /* Tone control register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 303 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 304 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 305 | * @brief I2C address Limiter 1 Attack/Release rate register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 306 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 307 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 308 | * Default value: 0x6A |

| davide.aliprandi@st.com | 4:77a26607bef6 | 309 | * [7:4] Limiter 1 Attack rate |

| davide.aliprandi@st.com | 4:77a26607bef6 | 310 | * [3:0] Limiter 1 release rate |

| davide.aliprandi@st.com | 4:77a26607bef6 | 311 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 312 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 313 | #define STA350BW_L1AR ((uint8_t)0x12) /* Limiter 1 Attack/Release rate register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 314 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 315 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 316 | * @brief I2C address Limiter 1 Attack/Release threshold register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 317 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 318 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 319 | * Default value: 0x69 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 320 | * [7:4] Limiter 1 Attack threshold |

| davide.aliprandi@st.com | 4:77a26607bef6 | 321 | * [3:0] Limiter 1 release threshold |

| davide.aliprandi@st.com | 4:77a26607bef6 | 322 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 323 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 324 | #define STA350BW_L1ATR ((uint8_t)0x13) /* Limiter 1 Attack/Release threshold register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 325 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 326 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 327 | * @brief I2C address Limiter 2 Attack/Release rate register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 328 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 329 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 330 | * Default value: 0x6A |

| davide.aliprandi@st.com | 4:77a26607bef6 | 331 | * [7:4] Limiter 2 Attack rate |

| davide.aliprandi@st.com | 4:77a26607bef6 | 332 | * [3:0] Limiter 2 Release rate |

| davide.aliprandi@st.com | 4:77a26607bef6 | 333 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 334 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 335 | #define STA350BW_L2AR ((uint8_t)0x14) /* Limiter 2 Attack/Release rate register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 336 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 337 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 338 | * @brief I2C address Limiter 2 Attack/Release threshold register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 339 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 340 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 341 | * Default value: 0x69 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 342 | * [7:4] Limiter 2 Attack threshold |

| davide.aliprandi@st.com | 4:77a26607bef6 | 343 | * [3:0] Limiter 2 release threshold |

| davide.aliprandi@st.com | 4:77a26607bef6 | 344 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 345 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 346 | #define STA350BW_L2ATR ((uint8_t)0x15) /* Limiter 2 Attack/Release threshold register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 347 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 348 | /* RAM download*/ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 349 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 350 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 351 | * @brief I2C address Coefficient address register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 352 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 353 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 354 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 355 | * [7:6] RESERVED |

| davide.aliprandi@st.com | 4:77a26607bef6 | 356 | * [5:0] RAM address |

| davide.aliprandi@st.com | 4:77a26607bef6 | 357 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 358 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 359 | #define STA350BW_CFADDR ((uint8_t)0x16) /* Coefficient address register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 360 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 361 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 362 | * @brief I2C address Coefficient b1 data register bits 23:16 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 363 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 364 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 365 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 366 | * [7:0] coefficient b1 bits 23:16 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 367 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 368 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 369 | #define STA350BW_B1CF1 ((uint8_t)0x17) /* Coefficient b1 data register bits 23:16 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 370 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 371 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 372 | * @brief I2C address Coefficient b1 data register bits 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 373 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 374 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 375 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 376 | * [7:0] coefficient b1 bits 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 377 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 378 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 379 | #define STA350BW_B1CF2 ((uint8_t)0x18) /* Coefficient b1 data register bits 15:8 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 380 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 381 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 382 | * @brief I2C address Coefficient b1 data register bits 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 383 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 384 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 385 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 386 | * [7:0] coefficient b1 bits 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 387 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 388 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 389 | #define STA350BW_B1CF3 ((uint8_t)0x19) /* Coefficient b1 data register bits 7:0 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 390 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 391 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 392 | * @brief I2C address Coefficient b2 data register bits 23:16 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 393 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 394 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 395 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 396 | * [7:0] coefficient b2 bits 23:16 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 397 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 398 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 399 | #define STA350BW_B2CF1 ((uint8_t)0x1A) /* Coefficient b2 data register bits 23:16 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 400 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 401 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 402 | * @brief I2C address Coefficient b2 data register bits 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 403 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 404 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 405 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 406 | * [7:0] coefficient b2 bits 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 407 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 408 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 409 | #define STA350BW_B2CF2 ((uint8_t)0x1B) /* Coefficient b2 data register bits 15:8 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 410 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 411 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 412 | * @brief I2C address Coefficient b2 data register bits 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 413 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 414 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 415 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 416 | * [7:0] Coefficient b2 data bits 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 417 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 418 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 419 | #define STA350BW_B2CF3 ((uint8_t)0x1C) /* Coefficient b2 data register bits 7:0 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 420 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 421 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 422 | * @brief I2C address Coefficient a1 data register bits 23:16 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 423 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 424 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 425 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 426 | * [7:0] Coefficient a1 data bits 23:16 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 427 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 428 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 429 | #define STA350BW_A1CF1 ((uint8_t)0x1D) /* Coefficient a1 data register bits 23:16 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 430 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 431 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 432 | * @brief I2C address Coefficient a1 data register bits 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 433 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 434 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 435 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 436 | * [7:0] Coefficient a1 data bits 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 437 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 438 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 439 | #define STA350BW_A1CF2 ((uint8_t)0x1E) /* Coefficient a1 data register bits 15:8 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 440 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 441 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 442 | * @brief I2C address Coefficient a1 data register bits 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 443 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 444 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 445 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 446 | * [7:0] Coefficient a1 data bits 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 447 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 448 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 449 | #define STA350BW_A1CF3 ((uint8_t)0x1F) /* Coefficient a1 data register bits 7:0 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 450 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 451 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 452 | * @brief I2C address Coefficient a2 data register bits 23:16 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 453 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 454 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 455 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 456 | * [7:0] Coefficient a2 data bits 23:16 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 457 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 458 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 459 | #define STA350BW_A2CF1 ((uint8_t)0x20) /* Coefficient a2 data register bits 23:16 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 460 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 461 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 462 | * @brief I2C address Coefficient a2 data register bits 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 463 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 464 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 465 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 466 | * [7:0] Coefficient a2 data bits 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 467 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 468 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 469 | #define STA350BW_A2CF2 ((uint8_t)0x21) /* Coefficient a2 data register bits 15:8 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 470 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 471 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 472 | * @brief I2C address Coefficient a2 data register bits 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 473 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 474 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 475 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 476 | * [7:0] Coefficient a2 data bits 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 477 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 478 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 479 | #define STA350BW_A2CF3 ((uint8_t)0x22) /* Coefficient a2 data register bits 7:0 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 480 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 481 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 482 | * @brief I2C address Coefficient b0 data register bits 23:16 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 483 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 484 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 485 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 486 | * [7:0] coefficient b0 bits 23:16 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 487 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 488 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 489 | #define STA350BW_B0CF1 ((uint8_t)0x23) /* Coefficient b0 data register bits 23:16 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 490 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 491 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 492 | * @brief I2C address Coefficient b0 data register bits 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 493 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 494 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 495 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 496 | * [7:0] Coefficient b0 data bits 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 497 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 498 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 499 | #define STA350BW_B0CF2 ((uint8_t)0x24) /* Coefficient b0 data register bits 15:8 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 500 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 501 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 502 | * @brief I2C address Coefficient b0 data register bits 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 503 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 504 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 505 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 506 | * [7:0] Coefficient b0 data bits 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 507 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 508 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 509 | #define STA350BW_B0CF3 ((uint8_t)0x25) /* Coefficient b0 data register bits 7:0 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 510 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 511 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 512 | * @brief I2C address Coefficient write/read control register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 513 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 514 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 515 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 516 | * [7:4] RESERVED |

| davide.aliprandi@st.com | 4:77a26607bef6 | 517 | * 3 RA read a complete set of coefficient |

| davide.aliprandi@st.com | 4:77a26607bef6 | 518 | * 2 R1 read only one coefficient |

| davide.aliprandi@st.com | 4:77a26607bef6 | 519 | * 1 WA write a complete set of coefficient |

| davide.aliprandi@st.com | 4:77a26607bef6 | 520 | * 0 W1 write only one coefficient |

| davide.aliprandi@st.com | 4:77a26607bef6 | 521 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 522 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 523 | #define STA350BW_CFUD ((uint8_t)0x26) /* Coefficient write/read control register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 524 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 525 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 526 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 527 | * @brief I2C address Variable max power correction 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 528 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 529 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 530 | * Default value: 0x1A |

| davide.aliprandi@st.com | 4:77a26607bef6 | 531 | * [7:0] Coefficient for Variable max power correction 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 532 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 533 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 534 | #define STA350BW_MPCC1 ((uint8_t)0x27) /* Variable max power correction 15:8 register*/ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 535 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 536 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 537 | * @brief I2C address Variable max power correction 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 538 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 539 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 540 | * Default value: 0x30 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 541 | * [7:0] Coefficient for Variable max power correction 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 542 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 543 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 544 | #define STA350BW_MPCC2 ((uint8_t)0x28) /* Variable max power correction 7:0 register*/ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 545 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 546 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 547 | * @brief I2C address Variable distortion compensation 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 548 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 549 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 550 | * Default value: 0xF3 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 551 | * [7:0] Coefficient for Variable distortion compensation 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 552 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 553 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 554 | #define STA350BW_DCC1 ((uint8_t)0x29) /* Variable distortion compensation 15:8 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 555 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 556 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 557 | * @brief I2C address Variable distortion compensation 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 558 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 559 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 560 | * Default value: 0x33 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 561 | * [7:0] Coefficient for Variable distortion compensation 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 562 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 563 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 564 | #define STA350BW_DCC2 ((uint8_t)0x2A) /* Variable distortion compensation 7:0 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 565 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 566 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 567 | * @brief I2C address Fault detect recovery constant register 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 568 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 569 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 570 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 571 | * [7:0] Fault detect recovery constant 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 572 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 573 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 574 | #define STA350BW_FDRC1 ((uint8_t)0x2B) /* Fault detect recovery constant register 15:8 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 575 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 576 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 577 | * @brief I2C address Fault detect recovery constant register 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 578 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 579 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 580 | * Default value: 0xC0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 581 | * [7:0] Fault detect recovery constant 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 582 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 583 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 584 | #define STA350BW_FDRC2 ((uint8_t)0x2C) /* Fault detect recovery constant register 7:0 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 585 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 586 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 587 | * @brief I2C address Status Register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 588 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 589 | * Read |

| davide.aliprandi@st.com | 4:77a26607bef6 | 590 | * Default value: 0x7F |

| davide.aliprandi@st.com | 4:77a26607bef6 | 591 | * 7 PLLUL PLL unlock |

| davide.aliprandi@st.com | 4:77a26607bef6 | 592 | * 6 FAULT Fault detected on bridge |

| davide.aliprandi@st.com | 4:77a26607bef6 | 593 | * 5 UVFAULT undervoltage fault |

| davide.aliprandi@st.com | 4:77a26607bef6 | 594 | * 4 OVFAULT overvoltage fault |

| davide.aliprandi@st.com | 4:77a26607bef6 | 595 | * 3 OCFAULT overcurrent fault |

| davide.aliprandi@st.com | 4:77a26607bef6 | 596 | * 2 OCWARN overcurrent warning |

| davide.aliprandi@st.com | 4:77a26607bef6 | 597 | * 1 TFAULT Thermal fault |

| davide.aliprandi@st.com | 4:77a26607bef6 | 598 | * 0 TWARN thermal warning |

| davide.aliprandi@st.com | 4:77a26607bef6 | 599 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 600 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 601 | #define STA350BW_STATUS ((uint8_t)0x2D) /* Status Register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 602 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 603 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 604 | * @brief I2C address EQ coefficients and DRC configuration register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 605 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 606 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 607 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 608 | * 7 XOB Crossover filter bypass |

| davide.aliprandi@st.com | 4:77a26607bef6 | 609 | * [6:5] RESERVED |

| davide.aliprandi@st.com | 4:77a26607bef6 | 610 | * [4:3] AMGC Anti-clipping and DRC preset |

| davide.aliprandi@st.com | 4:77a26607bef6 | 611 | * 2 RESERVED |

| davide.aliprandi@st.com | 4:77a26607bef6 | 612 | * [1:0] EQ RAM bank selector |

| davide.aliprandi@st.com | 4:77a26607bef6 | 613 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 614 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 615 | #define STA350BW_EQCFG ((uint8_t)0x31) /* EQ coefficients and DRC configuration register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 616 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 617 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 618 | * @brief I2C address Limiter 1 extended attack threshold register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 619 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 620 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 621 | * Default value: 0x30 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 622 | * 7 EATHEN1 Limiter 1 Extended Attack threshold enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 623 | * [6:0] EATH1 Limiter 1 Extended Attack threshold |

| davide.aliprandi@st.com | 4:77a26607bef6 | 624 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 625 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 626 | #define STA350BW_EATH1 ((uint8_t)0x32) /* Limiter 1 extended attack threshold register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 627 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 628 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 629 | * @brief I2C address Limiter 1 extended release threshold register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 630 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 631 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 632 | * Default value: 0x30 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 633 | * 7 ERTHEN1 Limiter 1 Extended Release threshold enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 634 | * [6:0] ERTH1 Limiter 1 Extended Release threshold |

| davide.aliprandi@st.com | 4:77a26607bef6 | 635 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 636 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 637 | #define STA350BW_ERTH1 ((uint8_t)0x33) /* Limiter 1 extended release threshold register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 638 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 639 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 640 | * @brief I2C address Limiter 2 extended attack threshold register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 641 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 642 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 643 | * Default value: 0x30 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 644 | * 7 EATHEN2 Limiter 2 Extended Attack threshold enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 645 | * [6:0] EATH2 Limiter 2 Extended Attack threshold |

| davide.aliprandi@st.com | 4:77a26607bef6 | 646 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 647 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 648 | #define STA350BW_EATH2 ((uint8_t)0x34) /* Limiter 2 extended attack threshold register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 649 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 650 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 651 | * @brief I2C address Limiter 2 extended release threshold register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 652 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 653 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 654 | * Default value: 0x30 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 655 | * 7 ERTHEN2 Limiter 2 Extended Release threshold enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 656 | * [6:0] ERTH2 Limiter 2 Extended Release threshold |

| davide.aliprandi@st.com | 4:77a26607bef6 | 657 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 658 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 659 | #define STA350BW_ERTH2 ((uint8_t)0x35) /* Limiter 2 extended release threshold register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 660 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 661 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 662 | * @brief I2C address Extended configuration register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 663 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 664 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 665 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 666 | * [7:6] MDRC MDRC or EQ DRC selector |

| davide.aliprandi@st.com | 4:77a26607bef6 | 667 | * 5 PS48DB Extended post-scale range |

| davide.aliprandi@st.com | 4:77a26607bef6 | 668 | * 4 Extended attack rate Limiter 1 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 669 | * 3 Extended attack rate Limiter 2 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 670 | * 2 Biquad 5 enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 671 | * 1 Biquad 6 enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 672 | * 0 Biquad 7 enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 673 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 674 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 675 | #define STA350BW_CONFX ((uint8_t)0x36) /* Extended configuration register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 676 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 677 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 678 | * @brief I2C address soft-volume up configuration register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 679 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 680 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 681 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 682 | * [7:6] RESERVED |

| davide.aliprandi@st.com | 4:77a26607bef6 | 683 | * 5 SVUPE Soft volume up enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 684 | * [4:0] SVUP Soft volume up coefficient |

| davide.aliprandi@st.com | 4:77a26607bef6 | 685 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 686 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 687 | #define STA350BW_SVCA ((uint8_t)0x37) /* soft-volume up configuration register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 688 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 689 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 690 | * @brief I2C address soft-volume down configuration register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 691 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 692 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 693 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 694 | * [7:6] RESERVED |

| davide.aliprandi@st.com | 4:77a26607bef6 | 695 | * 5 SVDWE Soft volume down enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 696 | * [4:0] SVDW Soft volume down coefficient |

| davide.aliprandi@st.com | 4:77a26607bef6 | 697 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 698 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 699 | #define STA350BW_SVCB ((uint8_t)0x38) /* soft-volume down configuration register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 700 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 701 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 702 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 703 | * @brief I2C address DRC RMS filter coefficient c0 23:16 register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 704 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 705 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 706 | * Default value: 0x01 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 707 | * [7:0] R_C0 DRC RMS filter coefficient c0 23:16 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 708 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 709 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 710 | #define STA350BW_RMS0A ((uint8_t)0x39) /* DRC RMS filter coefficient c0 23:16 register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 711 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 712 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 713 | * @brief I2C address DRC RMS filter coefficient c0 15:8 register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 714 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 715 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 716 | * Default value: 0xEE |

| davide.aliprandi@st.com | 4:77a26607bef6 | 717 | * [7:0] R_C0 DRC RMS filter coefficient c0 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 718 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 719 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 720 | #define STA350BW_RMS0B ((uint8_t)0x3A) /* DRC RMS filter coefficient c0 15:8 register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 721 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 722 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 723 | * @brief I2C address DRC RMS filter coefficient c0 7:0 register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 724 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 725 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 726 | * Default value: 0xFF |

| davide.aliprandi@st.com | 4:77a26607bef6 | 727 | * [7:0] R_C0 DRC RMS filter coefficient c0 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 728 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 729 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 730 | #define STA350BW_RMS0C ((uint8_t)0x3B) /* DRC RMS filter coefficient c0 7:0 register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 731 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 732 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 733 | * @brief I2C address DRC RMS filter coefficient c1 23:16 register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 734 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 735 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 736 | * Default value: 0x7E |

| davide.aliprandi@st.com | 4:77a26607bef6 | 737 | * [7:0] R_C1 DRC RMS filter coefficient c0 23:16 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 738 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 739 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 740 | #define STA350BW_RMS1A ((uint8_t)0x3C) /* DRC RMS filter coefficient c1 23:16 register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 741 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 742 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 743 | * @brief I2C address DRC RMS filter coefficient c1 15:8 register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 744 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 745 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 746 | * Default value: 0xC0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 747 | * [7:0] R_C1 DRC RMS filter coefficient c1 15:8 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 748 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 749 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 750 | #define STA350BW_RMS1B ((uint8_t)0x3D) /* DRC RMS filter coefficient c1 15:8 register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 751 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 752 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 753 | * @brief I2C address DRC RMS filter coefficient c1 7:0 register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 754 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 755 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 756 | * Default value: 0x26 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 757 | * [7:0] R_C0 DRC RMS filter coefficient c1 7:0 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 758 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 759 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 760 | #define STA350BW_RMS1C ((uint8_t)0x3E) /* DRC RMS filter coefficient c1 7:0 register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 761 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 762 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 763 | * @brief I2C address Extra volume resolution configuration register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 764 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 765 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 766 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 767 | * 7 VRESEN Extra volume resolution enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 768 | * 6 VRESTG Extra volume resolution update |

| davide.aliprandi@st.com | 4:77a26607bef6 | 769 | * [5:4] C3VR Channel 3 extra volume value |

| davide.aliprandi@st.com | 4:77a26607bef6 | 770 | * [3:2] C2VR Channel 2 extra volume value |

| davide.aliprandi@st.com | 4:77a26607bef6 | 771 | * [1:0] C1VR Channel 1 extra volume value |

| davide.aliprandi@st.com | 4:77a26607bef6 | 772 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 773 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 774 | #define STA350BW_EVOLRES ((uint8_t)0x3F) /* Extra volume resolution configuration register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 775 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 776 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 777 | * @brief I2C address Quantization error noise correction register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 778 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 779 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 780 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 781 | * 7 Quntization Noise shaping enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 782 | * 6 Quntization Noise shaping on biquad 7 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 783 | * 5 Quntization Noise shaping on biquad 6 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 784 | * 4 Quntization Noise shaping on biquad 5 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 785 | * 3 Quntization Noise shaping on biquad 4 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 786 | * 2 Quntization Noise shaping on biquad 3 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 787 | * 1 Quntization Noise shaping on biquad 2 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 788 | * 0 Quntization Noise shaping on biquad 1 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 789 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 790 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 791 | #define STA350BW_NSHAPE ((uint8_t)0x48) /* Quantization error noise correction register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 792 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 793 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 794 | * @brief I2C address Extended coefficient range up to -4...4 biquad 1-4 register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 795 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 796 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 797 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 798 | * [7:6] CXTB4 Extended coefficient on biquad 4 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 799 | * [5:4] CXTB3 Extended coefficient on biquad 3 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 800 | * [3:2] CXTB2 Extended coefficient on biquad 2 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 801 | * [1:0] CXTB1 Extended coefficient on biquad 1 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 802 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 803 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 804 | #define STA350BW_CXT_B4B1 ((uint8_t)0x49) /* Extended coefficient range up to -4...4 biquad 1-4 register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 805 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 806 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 807 | * @brief I2C address Extended coefficient range up to -4...4 biquad 5-7 register |

| davide.aliprandi@st.com | 4:77a26607bef6 | 808 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 809 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 810 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 811 | * [7:6] RESERVED |

| davide.aliprandi@st.com | 4:77a26607bef6 | 812 | * [5:4] CXTB7 Extended coefficient on biquad 7 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 813 | * [3:2] CXTB6 Extended coefficient on biquad 6 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 814 | * [1:0] CXTB5 Extended coefficient on biquad 5 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 815 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 816 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 817 | #define STA350BW_CXT_B7B5 ((uint8_t)0x4A) /* Extended coefficient range up to -4...4 biquad 5-7 register */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 818 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 819 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 820 | * @brief I2C address Miscellaneous register 1 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 821 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 822 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 823 | * Default value: 0x04 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 824 | * 7 RPDNEN Rate powerdown enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 825 | * 6 NSHHPEN Noise shaping feature enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 826 | * 5 BRIDGOFF Bridge immediate OFF |

| davide.aliprandi@st.com | 4:77a26607bef6 | 827 | * [4:3] RESERVED |

| davide.aliprandi@st.com | 4:77a26607bef6 | 828 | * 2 CPWMEN Channel PWM enable |

| davide.aliprandi@st.com | 4:77a26607bef6 | 829 | * [1:0] RESERVED |

| davide.aliprandi@st.com | 4:77a26607bef6 | 830 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 831 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 832 | #define STA350BW_MISC1 ((uint8_t)0x4B) /* Miscellaneous register 1 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 833 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 834 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 835 | * @brief I2C address Miscellaneous register 2 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 836 | * \code |

| davide.aliprandi@st.com | 4:77a26607bef6 | 837 | * Read/write |

| davide.aliprandi@st.com | 4:77a26607bef6 | 838 | * Default value: 0x00 |

| davide.aliprandi@st.com | 4:77a26607bef6 | 839 | * [7:5] RESERVED |

| davide.aliprandi@st.com | 4:77a26607bef6 | 840 | * [4:2] PNDLSL Power-down delay selector |

| davide.aliprandi@st.com | 4:77a26607bef6 | 841 | * [1:0] RESERVED |

| davide.aliprandi@st.com | 4:77a26607bef6 | 842 | * \endcode |

| davide.aliprandi@st.com | 4:77a26607bef6 | 843 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 844 | #define STA350BW_MISC2 ((uint8_t)0x4C) /* Miscellaneous register 2 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 845 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 846 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 847 | * @} |

| davide.aliprandi@st.com | 4:77a26607bef6 | 848 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 849 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 850 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 851 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 852 | /** @defgroup STA350BW_Main_parameter |

| davide.aliprandi@st.com | 4:77a26607bef6 | 853 | * @{ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 854 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 855 | #define STA350BW_EAPD_ON ((uint8_t)0x80) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 856 | #define STA350BW_EAPD_OFF ((uint8_t)0x00) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 857 | #define STA350BW_PWDN_OFF ((uint8_t)0x40) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 858 | #define STA350BW_PWDN_ON ((uint8_t)0x00) /* low power consumption */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 859 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 860 | #define STA350BW_MVOL_0dB ((uint8_t)0x00) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 861 | #define STA350BW_MVOL_MUTE ((uint8_t)0xFF) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 862 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 863 | * @} |

| davide.aliprandi@st.com | 4:77a26607bef6 | 864 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 865 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 866 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 867 | /** @defgroup STA350BW_Input_frequency_selection |

| davide.aliprandi@st.com | 4:77a26607bef6 | 868 | * @{ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 869 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 870 | #define STA350BW_Fs_32000 ((uint32_t)32000) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 871 | #define STA350BW_Fs_44100 ((uint32_t)44100) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 872 | #define STA350BW_Fs_48000 ((uint32_t)48000) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 873 | #define STA350BW_Fs_88200 ((uint32_t)88200) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 874 | #define STA350BW_Fs_96000 ((uint32_t)96000) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 875 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 876 | #define STA350BW_MCLK_256_LR_48K ((uint8_t)0x03) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 877 | #define STA350BW_MCLK_128_LR_48K ((uint8_t)0x04) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 878 | #define STA350BW_MCLK_256_LR_96K ((uint8_t)0x09) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 879 | #define STA350BW_MCLK_128_LR_96K ((uint8_t)0x0B) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 880 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 881 | * @} |

| davide.aliprandi@st.com | 4:77a26607bef6 | 882 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 883 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 884 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 885 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 886 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 887 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 888 | /** @defgroup STA350BW_mode_selection |

| davide.aliprandi@st.com | 4:77a26607bef6 | 889 | * @brief STA350BW mode configuration constants |

| davide.aliprandi@st.com | 4:77a26607bef6 | 890 | * @{ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 891 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 892 | #define STA350BW_STEREO_CONF ((uint8_t)0x00) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 893 | #define STA350BW_2SE_1BTL_CONF ((uint8_t)0x01) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 894 | #define STA350BW_STEREO_EXT_BRIDGE_CONF ((uint8_t)0x00) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 895 | #define STA350BW_MONOBTL_CONF ((uint8_t)0x11) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 896 | #define STA350BW_BINARY_CONF ((uint8_t)0x80) /* on registers 0E, 0F, 10 */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 897 | /** |

| davide.aliprandi@st.com | 4:77a26607bef6 | 898 | * @} |

| davide.aliprandi@st.com | 4:77a26607bef6 | 899 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 900 | |

| davide.aliprandi@st.com | 4:77a26607bef6 | 901 | /** @defgroup STA350BW_DSP_option_selection |

| davide.aliprandi@st.com | 4:77a26607bef6 | 902 | * @brief STA350BW constants related to data path management |

| davide.aliprandi@st.com | 4:77a26607bef6 | 903 | * @{ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 904 | */ |

| davide.aliprandi@st.com | 4:77a26607bef6 | 905 | #define STA350BW_DSPB ((uint8_t)0x00) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 906 | #define STA350BW_C1EQBP ((uint8_t)0x01) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 907 | #define STA350BW_C2EQBP ((uint8_t)0x02) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 908 | #define STA350BW_C1TCB ((uint8_t)0x03) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 909 | #define STA350BW_C2TCB ((uint8_t)0x04) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 910 | #define STA350BW_C1VBP ((uint8_t)0x05) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 911 | #define STA350BW_C2VBP ((uint8_t)0x06) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 912 | #define STA350BW_HPB ((uint8_t)0x07) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 913 | #define STA350BW_DEMP ((uint8_t)0x08) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 914 | #define STA350BW_BQL ((uint8_t)0x09) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 915 | #define STA350BW_BQ5 ((uint8_t)0x0A) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 916 | #define STA350BW_BQ6 ((uint8_t)0x0B) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 917 | #define STA350BW_BQ7 ((uint8_t)0x0C) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 918 | #define STA350BW_EXT_RANGE_BQ1 ((uint8_t)0x0D) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 919 | #define STA350BW_EXT_RANGE_BQ2 ((uint8_t)0x0E) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 920 | #define STA350BW_EXT_RANGE_BQ3 ((uint8_t)0x0F) |

| davide.aliprandi@st.com | 4:77a26607bef6 | 921 | #define STA350BW_EXT_RANGE_BQ4 ((uint8_t)0x10) |