Important changes to forums and questions

All forums and questions are now archived. To start a new conversation or read the latest updates go to forums.mbed.com.

6 years, 11 months ago.

Trick to using SPI on MAX32630FTHR?

I am having a strange problem trying to use SPI on the board. I get SPI cycles with SCK and correct data on MOSI but the data on MISO is not read correctly. I wrote this very simple test program based on the mbed example.

/media/uploads/danjulio/main.cpp

This produces the following output. The first byte is what is output to MOSI. The second byte is what is read from MISO.

Am I doing something wrong or is there some issue with the SPI implementation for the MAX32630FTHR?

0x 0 : 0x80

0x 1 : 0x80

0x 2 : 0x81

0x 3 : 0x81

0x 4 : 0x82

0x 5 : 0x82

0x 6 : 0x83

0x 7 : 0x83

0x 8 : 0x84

0x 9 : 0x84

0x a : 0x85

0x b : 0x85

0x c : 0x86

0x d : 0x86

0x e : 0x87

0x f : 0x87

0x10 : 0x88

0x11 : 0x88

0x12 : 0x89

0x13 : 0x89

0x14 : 0x8a

0x15 : 0x8a

0x16 : 0x8b

0x17 : 0x8b

0x18 : 0x8c

0x19 : 0x8c

0x1a : 0x8d

0x1b : 0x8d

0x1c : 0x8e

0x1d : 0x8e

0x1e : 0x8f

0x1f : 0x8f

0x20 : 0x90

0x21 : 0x90

0x22 : 0x91

0x23 : 0x91

0x24 : 0x92

0x25 : 0x92

0x26 : 0x93

0x27 : 0x93

0x28 : 0x94

0x29 : 0x94

0x2a : 0x95

0x2b : 0x95

0x2c : 0x96

0x2d : 0x96

0x2e : 0x97

0x2f : 0x97

0x30 : 0x98

0x31 : 0x98

0x32 : 0x99

0x33 : 0x99

0x34 : 0x9a

0x35 : 0x9a

0x36 : 0x9b

0x37 : 0x9b

0x38 : 0x9c

0x39 : 0x9c

0x3a : 0x9d

0x3b : 0x9d

0x3c : 0x9e

0x3d : 0x9e

0x3e : 0x9f

0x3f : 0x9f

0x40 : 0xa0

0x41 : 0xa0

0x42 : 0xa1

0x43 : 0xa1

0x44 : 0xa2

0x45 : 0xa2

0x46 : 0xa3

0x47 : 0xa3

0x48 : 0xa4

0x49 : 0xa4

0x4a : 0xa5

0x4b : 0xa5

0x4c : 0xa6

0x4d : 0xa6

0x4e : 0xa7

0x4f : 0xa7

0x50 : 0xa8

0x51 : 0xa8

0x52 : 0xa9

0x53 : 0xa9

0x54 : 0xaa

0x55 : 0xaa

0x56 : 0xab

0x57 : 0xab

0x58 : 0xac

0x59 : 0xac

0x5a : 0xad

0x5b : 0xad

0x5c : 0xae

0x5d : 0xae

0x5e : 0xaf

0x5f : 0xaf

0x60 : 0xb0

0x61 : 0xb0

0x62 : 0xb1

0x63 : 0xb1

0x64 : 0xb2

0x65 : 0xb2

0x66 : 0xb3

0x67 : 0xb3

0x68 : 0xb4

0x69 : 0xb4

0x6a : 0xb5

0x6b : 0xb5

0x6c : 0xb6

0x6d : 0xb6

0x6e : 0xb7

0x6f : 0xb7

0x70 : 0xb8

0x71 : 0xb8

0x72 : 0xb9

0x73 : 0xb9

0x74 : 0xba

0x75 : 0xba

0x76 : 0xbb

0x77 : 0xbb

0x78 : 0xbc

0x79 : 0xbc

0x7a : 0xbd

0x7b : 0xbd

0x7c : 0xbe

0x7d : 0xbe

0x7e : 0xbf

0x7f : 0xbf

0x80 : 0xc0

0x81 : 0xc0

0x82 : 0xc1

0x83 : 0xc1

0x84 : 0xc2

0x85 : 0xc2

0x86 : 0xc3

0x87 : 0xc3

0x88 : 0xc4

0x89 : 0xc4

0x8a : 0xc5

0x8b : 0xc5

0x8c : 0xc6

0x8d : 0xc6

0x8e : 0xc7

0x8f : 0xc7

0x90 : 0xc8

0x91 : 0xc8

0x92 : 0xc9

0x93 : 0xc9

0x94 : 0xca

0x95 : 0xca

0x96 : 0xcb

0x97 : 0xcb

0x98 : 0xcc

0x99 : 0xcc

0x9a : 0xcd

0x9b : 0xcd

0x9c : 0xce

0x9d : 0xce

0x9e : 0xcf

0x9f : 0xcf

0xa0 : 0xd0

0xa1 : 0xd0

0xa2 : 0xd1

0xa3 : 0xd1

0xa4 : 0xd2

0xa5 : 0xd2

0xa6 : 0xd3

0xa7 : 0xd3

0xa8 : 0xd4

0xa9 : 0xd4

0xaa : 0xd5

0xab : 0xd5

0xac : 0xd6

0xad : 0xd6

0xae : 0xd7

0xaf : 0xd7

0xb0 : 0xd8

0xb1 : 0xd8

0xb2 : 0xd9

0xb3 : 0xd9

0xb4 : 0xda

0xb5 : 0xda

0xb6 : 0xdb

0xb7 : 0xdb

0xb8 : 0xdc

0xb9 : 0xdc

0xba : 0xdd

0xbb : 0xdd

0xbc : 0xde

0xbd : 0xde

0xbe : 0xdf

0xbf : 0xdf

0xc0 : 0xe0

0xc1 : 0xe0

0xc2 : 0xe1

0xc3 : 0xe1

0xc4 : 0xe2

0xc5 : 0xe2

0xc6 : 0xe3

0xc7 : 0xe3

0xc8 : 0xe4

0xc9 : 0xe4

0xca : 0xe5

0xcb : 0xe5

0xcc : 0xe6

0xcd : 0xe6

0xce : 0xe7

0xcf : 0xe7

0xd0 : 0xe8

0xd1 : 0xe8

0xd2 : 0xe9

0xd3 : 0xe9

0xd4 : 0xea

0xd5 : 0xea

0xd6 : 0xeb

0xd7 : 0xeb

0xd8 : 0xec

0xd9 : 0xec

0xda : 0xed

0xdb : 0xed

0xdc : 0xee

0xdd : 0xee

0xde : 0xef

0xdf : 0xef

0xe0 : 0xf0

0xe1 : 0xf0

0xe2 : 0xf1

0xe3 : 0xf1

0xe4 : 0xf2

0xe5 : 0xf2

0xe6 : 0xf3

0xe7 : 0xf3

0xe8 : 0xf4

0xe9 : 0xf4

0xea : 0xf5

0xeb : 0xf5

0xec : 0xf6

0xed : 0xf6

0xee : 0xf7

0xef : 0xf7

0xf0 : 0xf8

0xf1 : 0xf8

0xf2 : 0xf9

0xf3 : 0xf9

0xf4 : 0xfa

0xf5 : 0xfa

0xf6 : 0xfb

0xf7 : 0xfb

0xf8 : 0xfc

0xf9 : 0xfc

0xfa : 0xfd

0xfb : 0xfd

0xfc : 0xfe

0xfd : 0xfe

0xfe : 0xff

Question relating to:

2 Answers

6 years, 11 months ago.

The current version of the MAX32630FTHR board is shipping with the MAX32630 rev A2. These parts only support SPI mode 0. You can find the details in the errata which is available in the datasheet link on the product page: https://www.maximintegrated.com/en/products/digital/microcontrollers/MAX32630.html

6 years, 11 months ago.

SPI line MISO is Master In Slave out and is usually linked with a CS (Chip select) on the mating SPI device. Would you have such a pin on your external SPI device ? If yes, that pin should then be connected to a free GPIO pin on your mbed board and respectively you will need to toggle this CS pin to enable the SPI device for such communications. Often called Slave Select.

See the example here:

https://developer.mbed.org/handbook/SPI

Note line 4 and the use of the DigitalOut definition for cs(port pin); You will need to do the same. Proceed to test this configuration and post your results. If still no luck, then post more details on the SPI widget you are testing including wiring diagram.

---

Got it. When you monitor the traffic on MOSI - is this MOSI pin mated with the local MISO pin ? It will be worthwhile to review the MOSI pin without MISO connection and then again with the MISO pin connected.

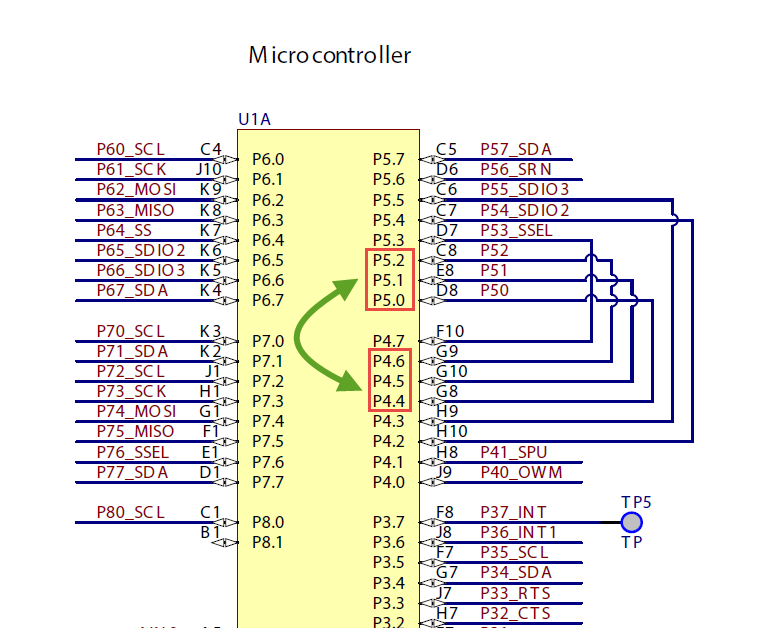

Perhaps the MISO results are tainted due to the port sharing method used by this Maxim board. See the schematic to note the same SPI port pins are being used by port P4.x. Confirm that each of the P4.x block of pins are hi-z. Although not a believer of hacking up original tools, you could even cut the trace between the MISO for your SPI Master (P5.2) and the shared SPI Slave P4.6 pin to isolate the two traces.

Thanks for the reply Sanjiv. I have experience using SPI. I originally tried to communicate with a MAX31865 RTD temperature amplifier chip using a software controlled CS line. My application will ultimately have two SPI peripherals so I did not define CS in the SPI object enumeration. I could see that MOSI data to the slave was ok (and I was driving CS correctly). However the data seen by the CPU from MISO was incorrect (I could see using an oscilloscope that it was being correctly driven by the 31865). So I wrote this very basic program just to test the SPI driver. It has no CS signal because that is not needed. I simply loop MOSI back to MISO with a wire and view the transactions on the scope as well (they are correct). The CPU should see the data it drives out. However as you can see, this data is incorrect.

posted by 21 May 2017Good suggestions. Thank you. I had tried setting P4.6 to a DigitalIn with no luck. Upon your suggestion, I set all three secondary ports to inputs (P4.4, P4.5, P4.6) but it didn't change anything either. It's not clear where I could cut to physically disconnect those signals and I am hesitant to try that because I have only one board and my fat fingers would probably make a mess of it. If I do not tie MISO to MOSI then I always read 0xFF as the input.

I have found what appears to be MAX32630FTHR specific support code including SPI code. However I haven't tried to parse through it since it looks moderately complex and will require diving into the chip spec.

posted by 23 May 2017Dan - do you receive the same echo values if you change the SPI mode to be 0 ? Greg (works for Maxim) and he is noting that the silicon appears to be only supportive of SPI Mode 0 (not 1, 2, 3). Consider to change your code to SPI mode 0 and perform the MISO & MOSI connection to test. Curious on your results.

-

Change:

spi.format(8, 1);

to

spi.format(8, 0);

posted by 23 May 2017